Hyper-threading

Hyper-threading (officiellement appelée Hyper-Threading Technology (HTT) ou HT Technology (HT)) est la mise en œuvre par l'entreprise Intel du simultaneous multithreading (SMT) à deux voies dans ses microprocesseurs. Le premier modèle grand public de la gamme à en bénéficier fut le Pentium 4 Northwood cadencé à 3,06 GHz. Le Xeon Northwood en bénéficia auparavant.

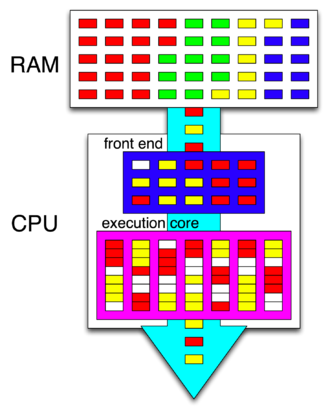

Schématiquement, l’hyper-threading consiste à créer deux processeurs logiques sur une seule puce, chacun doté de ses propres registres de données et de contrôle, et d’un contrôleur d’interruptions particulier. Ces deux unités partagent les éléments du cœur de processeur, le cache et le bus système. Ainsi, deux sous-processus peuvent être traités simultanément par le même processeur. Cette technique multitâche permet d’utiliser au mieux les ressources du processeur en garantissant que des données lui soient envoyées en masse. Elle permet aussi d’améliorer les performances en cas de défauts de cache (cache misses).

Performances

[modifier | modifier le code]Les avantages de l’hyper-threading sont les suivants :

- amélioration du support de code multi-threadé ;

- gestion de plusieurs threads en même temps ;

- meilleur temps de réaction, meilleur temps de réponse ;

- dans le cas d’un serveur informatique, augmentation du nombre d’utilisateurs possible.

Selon Intel, la première mise en œuvre n’utilisait que 5 % de surface supplémentaire sur le support physique par rapport à un processeur normal. Cette approche offrait un gain en performance variant entre 15 et 30 % selon les applications. Intel affirme que ce gain va jusqu’à 30 % par rapport à un Pentium 4 sans cette technologie[1].

Toutefois, les performances varient sensiblement selon les applications. Dans certains cas (peu fréquents), l’exécution s’avère même plus lente quand l’hyper-threading est activé. Cette perte est causée par le système de replay (en) présent dans le Pentium 4 qui met en attente certaines instructions qui ne remplissent pas les conditions nécessaires à leur exécution. Il empêche l’hyper-threading d’exécuter d’autres tâches.

Les performances peuvent également être affectées par des effets liés à la mémoire cache. Par exemple avec un processeur comportant 512 ko de cache et des processus opérant sur 400 ko de données, on peut distinguer deux cas :

- les deux processus tournent individuellement, le processeur est capable de mettre en cache les données ;

- quand les deux processus tournent en même temps, ils nécessitent 800 ko de cache, les défauts de cache seront fréquents.

Les défauts de cache dégradent fortement les performances sur les systèmes modernes et cela peut affecter les gains obtenus avec l’hyper-threading de manière significative.

Sécurité

[modifier | modifier le code]En , le programmeur[2] Colin Percival a publié un document nommé Cache Missing for Fun and Profit[3] où il démontre comment un thread malveillant, lancé avec des privilèges limités, pourrait en théorie accéder à des informations provenant d’un autre thread. Ce genre d’attaques, nommées attaques par canaux auxiliaires, permettent d’obtenir des informations secrètes comme des clés de chiffrement.

Références

[modifier | modifier le code]- « How to Determine the Effectiveness of Hyper-Threading Technology with... », sur Intel (consulté le ).

- (en) « The Setup - Colin Percival », sur usesthis.com via Wikiwix (consulté le ).

- (en) [PDF].