Sunny Cove

| Production | Septembre 2019 |

|---|---|

| Concepteur | Intel |

| Fabricant | Intel |

| Niveau 1 |

80 ko par coeur : 32 ko instructions + 48 ko données |

|---|---|

| Niveau 2 | 512 ko par coeur |

| Niveau 3 | 2 Mo par coeur |

| Finesse de gravure | Procédé Intel FinFET 10 nm |

|---|

| Architecture | x86, x86-64 |

|---|---|

| Extensions | AES-NI, CLMUL, RDRAND, SHA (en), TXT (en), SGX (en), MMX, SSE, SSE2, SSE3, SSSE3, SSE4, SSE4.1, SSE4.2, AVX, AVX2, AVX-512, FMA3, VT-x, VT-d |

| Variantes |

|

|---|

Sunny Cove est le nom de code d’une microarchitecture de processeur développée par Intel, publiée pour la première fois en septembre 2019. Elle succède à la microarchitecture Palm Cove (en) et est fabriquée à l’aide du nœud de procédé 10 nm d’Intel[1]. La microarchitecture est implémentée dans les processeurs Intel Core de 10e génération pour PC portables (nom de code Ice Lake) et les processeurs de serveurs Xeon Scalable de 3e génération (nom de code Ice Lake-SP). Les processeurs pour PC portables Intel Core de 10e génération sont sortis en septembre 2019, tandis que les processeurs pour serveurs Xeon sont sortis le 6 avril 2021[2].

Il n’y a aucun PC de bureau proposant Sunny Cove. Cependant, une variante nommée Cypress Cove est utilisée pour les processeurs pour PC de bureau Intel Core de 11e génération (nom de code Rocket Lake). Cypress Cove est une version de la microarchitecture Sunny Cove rétroportée sur le nœud de procédé 14 nm d’Intel[3].

Le successeur direct de la microarchitecture Sunny Cove est la microarchitecture Willow Cove, qui équipe les processeurs pour PC portables Intel Core de 11e génération[4].

Caractéristiques

[modifier | modifier le code]Sunny Cove a été conçu par l’équipe de conception de processeurs d’Intel à Haïfa, en Israël[5],[6].

Intel a publié des détails sur Ice Lake et sa microarchitecture, Sunny Cove, lors de l’Intel Architecture Day en décembre 2018, déclarant que les cœurs Sunny Cove se concentreraient sur les performances d’un seul thread, de nouvelles instructions et des améliorations de l’évolutivité. Intel a déclaré que les améliorations de performances seraient obtenues en rendant le coeur « plus profond, plus large et plus intelligent »[7].

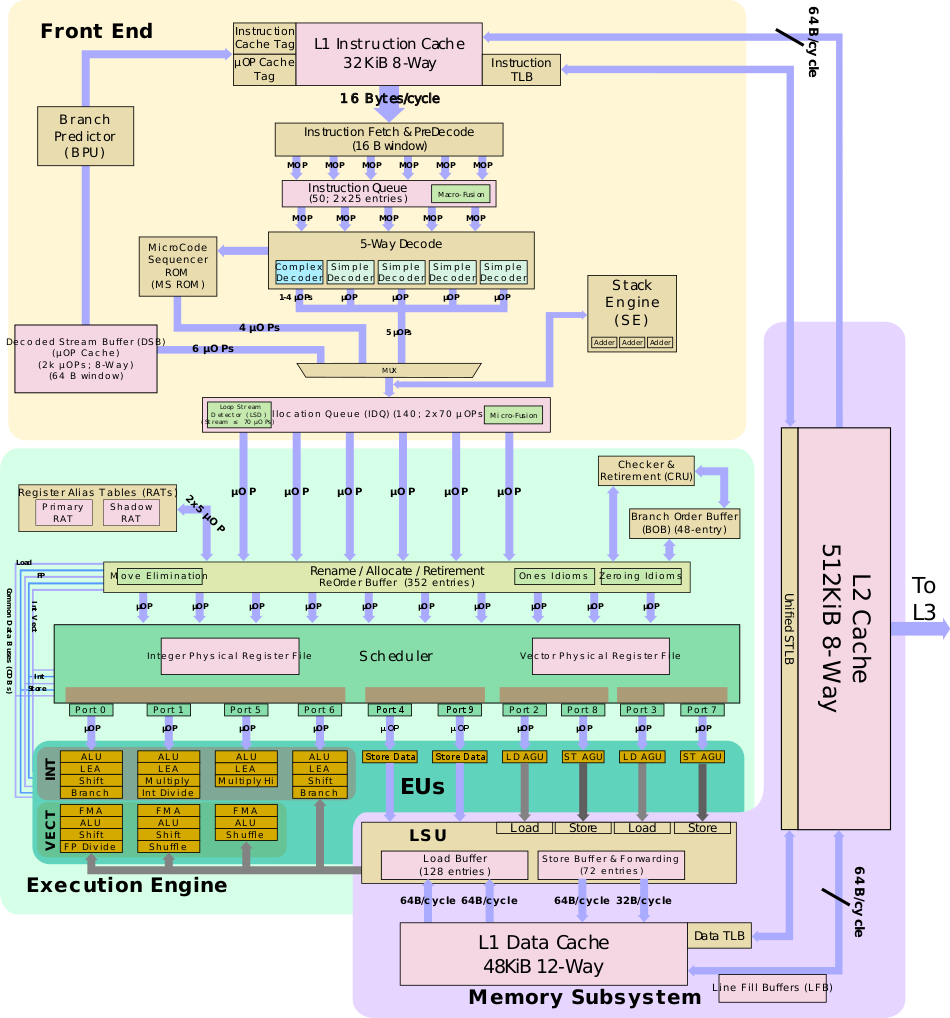

Sunny Cove se caractérise par une augmentation de 50 % de la taille du cache de données L1, un cache L2 plus important dépendant de la taille du produit, un cache de μOP plus important et un TLB de deuxième niveau plus important. La largeur du cœur a également augmenté, en augmentant le nombre de ports d’exécution de huit à dix et en doublant la bande passante du stockage dans L1. La largeur d’allocation a également augmenté, passant de quatre à cinq. Le schéma de pagination à cinq niveaux (en) prend en charge un espace d’adressage linéaire jusqu’à 57 bits et un espace d’adressage physique jusqu’à 52 bits, ce qui augmente l’espace de mémoire virtuelle de 256 téraoctets à 128 pétaoctets et la mémoire physique adressable de 64 téraoctets à 4 pétaoctets[7],[8].

Améliorations de l'architecture par rapport à Skylake

[modifier | modifier le code]- Augmentation de 18 % en moyenne de l'IPC par rapport à Skylake de 2015 tournant à la même fréquence et avec la même configuration mémoire[9],[10]

- Taille du cache de données L1 accrue : 48 ko par coeur (contre 32 ko)

- Cache L2 : 512 ko par coeur[11] (contre 256 ko)

- Décodeur d'instructions plus large (Skylake : décodeur à 4 voies, 3 simples + 1 complexe - Sunny Cove : décodeur à 5 voies, 4 simple + 1 complexe)

- Cache de micro-opérations plus grand (2304 entrées, contre 1536)

- Tampon de réorganisation plus grand (352 entrées, contre 224)

- Planificateur (Scheduler)

- Planificateur 1,65 fois plus large (160 entrées, contre 97)

- Répartition plus large (10 ports d'exécution au lieu de 8)

- Fichier de registres d'entiers 1,55 fois plus grand (280 entrées, contre 180)

- Fichier de registres vectoriels 1,33 plus grand (224 entrées, contre 168)

- Queues de planification distribuées (4 queues de planification, contre 2)

- Dynamic Tuning 2.0 qui permet au CPU de rester plus longtemps en fréquence Turbo[12],[13]

- Accélération hardware des opérations SHA (Secure Hash Algorithms)

- Nouveaux sous-ensembles d'instructions AVX-512 : VPOPCNTDQ, VBMI2, BITALG, VPCLMULQDQ, GFNI, VAES, VNNI

- Intel Deep Learning Boost (en), utilisé pour l'accélération de l'inférence en apprentissage automatique/intelligence artificielle[14],[13]

Cypress Cove

[modifier | modifier le code]| Production | 30 mars 2021 |

|---|---|

| Concepteur | Intel |

| Fabricant | Intel |

| Niveau 1 |

80 ko par coeur :

|

|---|---|

| Niveau 2 | 512 ko par coeur |

| Niveau 3 | 2 Mo par coeur |

| Finesse de gravure | Procédé Intel FinFET 14 nm |

|---|

| Architecture | x86, x86-64 |

|---|---|

| Extensions | MMX, SSE, SSE2, SSE3, SSSE3, SSE4, SSE4.1, SSE4.2, AVX, AVX2, AVX-512, FMA3, AES, CLMUL, RDRAND, SHA (en), TXT (en), VT-d, VT-x |

| Variantes | Rocket Lake |

|---|

Cypress Cove est une microarchitecture de CPU basée sur la microarchitecture Sunny Cove conçue en 10 nm, rétroportée en 14 nm. Elle succède à la microarchitecture Skylake et est fabriquée avec le nœud de procédé 14 nm d'Intel. Cypress Cove est identique à Sunny Cove, en dehors de quelques améliorations et changements[15]. Notamment, la latence du cache de données L1 a été réduite de cinq cycles sur Sunny Cove à seulement trois cyles sur Cypress Cove en passant d'une associativité 8 voies sur Sunny Cove à une associativité 12 voies sur Cypress Cove. Intel revendique une augmentation de 19 % de l'IPC des processeurs Rocket Lake basés sur Cypress Cove comparé à Comet Lake[15],[16].

Cypress Cove est implémenté sur les processeurs pour PC de bureau Intel Core de 11e génération (nom de code Rocket Lake). Rocket Lake et sa microarchitecture ont été décrits pour la première fois ent novembre 2020[3], et sont sortis le 30 mars 2021[17],[18].

Le jeu d'extensions SGX (en) est supprimé de Rocket Lake.

Références

[modifier | modifier le code]- (en-US) Anthony Garreffa, « Intel teases its Ice Lake & Tiger Lake family, 10nm for 2018 and 2019 », sur TweakTown, (consulté le )

- (en-US) « Media Alert: Intel to Launch 3rd Gen Intel Xeon Scalable Portfolio », sur Intel Newsroom, Santa Clara, CA, (consulté le )

- (en-US) Ian Cutress, « Intel's 11th Gen Core Rocket Lake Detailed: Ice Lake Core with Xe Graphics », sur AnandTech, (consulté le )

- (en-US) Ian Cutress, « Intel's 11th Gen Core Tiger Lake SoC Detailed: SuperFin, Willow Cove and Xe-LP », sur AnandTech, (consulté le )

- (he) « Intel launches 10th gen core processor developed in Israel », sur en.globes.co.il, (consulté le )

- (en-US) Shoshanna Solomon, « Intel launches new processors that bring AI to the PC, sired by Haifa team », sur The Times of Israel, (consulté le )

- (en-US) Ian Cutress, « Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86 », sur AnandTech, (consulté le )

- (en-US) « 5-Level Paging and 5-Level EPT », sur Intel,

- (en-US) David Schor, « Intel Sunny Cove Core To Deliver A Major Improvement In Single-Thread Performance, Bigger Improvements To Follow », sur WikiChip Fuse, (consulté le )

- (en-US) David Schor, « Intel Announces 10th Gen Core Processors Based On 10nm Ice Lake, Now Shipping », sur WikiChip Fuse, (consulté le )

- (en-US) « Intel Ice Lake 10nm CPU Benchmark Leak Shows More Cache, Higher Performance », HotHardware, (consulté le )

- (en-US) « Dynamic Tuning - Intel - WikiChip », sur WikiChip (consulté le )

- (en-US) Ian Cutress, « Examining Intel's Ice Lake Processors: Taking a Bite of the Sunny Cove Microarchitecture », sur AnandTech, (consulté le )

- (en-US) « Intel® Deep Learning Boost », sur Intel AI (consulté le )

- (en-US) Ian Cutress, « Intel Rocket Lake (14nm) Review: Core i9-11900K, Core i7-11700K, and Core i5-11600K », sur AnandTech, (consulté le )

- (en-US) « 11th Gen Intel Core: Unmatched Overclocking, Game Performance », sur Intel Newsroom, (consulté le )

- (en-US) Paul Alcorn, « Intel Rocket Lake Price, Benchmarks, Specs and Release Date, All We Know », sur Tom's Hardware, (consulté le )

- (en-US) Gordon Mah Ung, « Intel's new 11th-gen Rocket Lake-S CPU: Everything you need to know », sur PCWorld, (consulté le )