Category:OR gates

Jump to navigation

Jump to search

Digital logic gate type | |||||

| Upload media | |||||

| Subclass of | |||||

|---|---|---|---|---|---|

| |||||

Subcategories

This category has the following 10 subcategories, out of 10 total.

4

- 4071 (CMOS) (8 F)

- 4072 (CMOS) (2 F)

- 4075 (CMOS) (4 F)

- 4078 (CMOS) (1 F)

C

- CMOS OR gates (2 F)

O

- OR gate symbols (59 F)

W

- Wired OR gates (21 F)

Media in category "OR gates"

The following 70 files are in this category, out of 70 total.

-

1 or gate plus 1 and gate.svg 610 × 287; 9 KB

-

12-input OR gate via cascade of OR gates.svg 300 × 162; 6 KB

-

12-input OR gate via NOR and NAND gates.svg 257 × 162; 5 KB

-

15йцуке.JPG 208 × 284; 10 KB

-

2. Teorema.png 620 × 166; 5 KB

-

2. Theorem.svg 512 × 91; 1 KB

-

2014-01-15 08-42-37 electronique-site-plutons porte-logique.jpg 1,950 × 1,286; 1.04 MB

-

220px - Square Wave OR.JPG 220 × 66; 3 KB

-

2ИЛИ-НЕ3.jpg 448 × 320; 22 KB

-

And-or-not-Esquema.jpg 896 × 293; 86 KB

-

ApplicationSimplificationd'uncircuitlogiquePage14Image1.svg 600 × 120; 34 KB

-

ApplicationSimplificationd'uncircuitlogiquePage14Image2.svg 600 × 500; 368 KB

-

CPT-logic-gate building circuit.svg 421 × 528; 22 KB

-

CPT-logic-gate conversion (-A+-B).C.svg 435 × 210; 17 KB

-

CPT-logic-gate conversion (A.B)+C.svg 290 × 100; 12 KB

-

CPT-logic-gate conversion (A.¬B)(+)(B.C).svg 385 × 174; 19 KB

-

CPT-logic-gate conversion (B+D).(¬A+¬B).svg 416 × 282; 22 KB

-

CPT-logic-gate conversion ¬((A.B).(C+¬D)).svg 398 × 169; 32 KB

-

CPT-logic-gate conversion ¬(A.+B).C.svg 256 × 95; 23 KB

-

CPT-Logic-OR-Switch.svg 682 × 514; 9 KB

-

CPU OR.PNG 450 × 250; 6 KB

-

Disjunkce.png 110 × 158; 1 KB

-

Domino logic gate.jpg 2,549 × 3,065; 610 KB

-

Domino Logic Gates.svg 319 × 177; 26 KB

-

Fonctions logiques(4-a).png 161 × 111; 754 bytes

-

Fonctions logiques(4-d).png 240 × 420; 5 KB

-

Funcion logica O.PNG 482 × 149; 3 KB

-

Log-ili-ne.JPG 250 × 250; 6 KB

-

Logic-OR.svg 303 × 221; 13 KB

-

Logische Verknuepfung OR.svg 2,000 × 1,200; 80 KB

-

Masques 1.png 550 × 183; 16 KB

-

MFrey A or B or C.svg 1,200 × 1,000; 7 KB

-

MFrey A or B.svg 1,200 × 700; 5 KB

-

MFrey C or B or A.svg 1,200 × 1,000; 7 KB

-

MFrey Not A NAnd Not B.svg 150 × 80; 17 KB

-

Negative-Positive Logic (2 gates).PNG 800 × 128; 10 KB

-

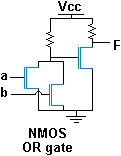

NMOS OR gate.png 121 × 156; 1 KB

-

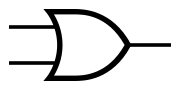

OR ANSI.svg 100 × 50; 675 bytes

-

OR from NAND.svg 200 × 100; 19 KB

-

OR gate with two transistors and a NOT gate.png 644 × 358; 14 KB

-

OR gate.png 759 × 396; 8 KB

-

OR Using NAND.svg 346 × 157; 12 KB

-

OR using NAND.svg 229 × 100; 12 KB

-

Or-gate-en.svg 500 × 180; 4 KB

-

OR-Gatter.png 800 × 544; 7 KB

-

OR-Gatter.svg 800 × 514; 5 KB

-

OR-poort kontakt equivalent.png 221 × 90; 636 bytes

-

OR-poort relais.png 210 × 195; 2 KB

-

OR-switch.PNG 191 × 134; 2 KB

-

OR3 aus OR2 DIN40700.png 90 × 146; 466 bytes

-

OR4Va.png 262 × 166; 2 KB

-

OR4Vb.png 336 × 137; 2 KB

-

Ou-nand.png 206 × 113; 2 KB

-

PMOS OR gate.png 233 × 334; 3 KB

-

Porte logique OU (jeu de la vie).jpg 202 × 267; 8 KB

-

Puerta lógica OR biología sintética.png 1,065 × 236; 77 KB

-

Puerta OR con transistores.jpg 584 × 448; 18 KB

-

Relay or.svg 200 × 150; 11 KB

-

Schema OR poort.jpg 529 × 374; 40 KB

-

Skakelaar or.png 153 × 116; 1 KB

-

Switch alternate and or.png 575 × 198; 4 KB

-

Switch circuit or.png 153 × 116; 1 KB

-

Switch circuit or.svg 153 × 116; 8 KB

-

SynBioCirc-OrLogicGate.jpg 1,065 × 236; 120 KB

-

Transistor OR Gate.png 380 × 543; 26 KB

-

TrippleOr at 3 4 5.svg 582 × 150; 10 KB

-

USSR K155LL2 (=75453).jpg 4,000 × 3,000; 3.16 MB

-

Venn-OR-static.png 1,032 × 396; 192 KB

-

Venn-OR.gif 480 × 304; 4.25 MB

-

ЭСЛ 4ИЛИ.svg 360 × 245; 9 KB